## **DFM** analysis report\_JLCDFM

**Project Outputs for Barrel Jack DCDC** File name: Project.zip

Report generated at: 2024-09-09 16:56:47

> PCB layers: 4Layer

PCB size:

✓ PCB DFM SMT DFM Analyze project:

7.48x2.82cm

(Detect clearance of vias to pads)

Analyze project

No

Analysis results

| Analyze project                                                                              | Analysis results              | PCB screenshot | Layer distribution                                                                                                                                | Statistics                           |

|----------------------------------------------------------------------------------------------|-------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Sharp trace corner (Check for sharp corners in traces)                                       | No                            | No             | No                                                                                                                                                | Danger: 0 Warning: 0 Good: 0         |

| BGA pad Check BGA pads on the board)                                                         | No                            | No             | No                                                                                                                                                | Danger: 0 Warning: 0 Good: 0         |

| Via placed within a pad (Check if there is a via placed within a pad)                        | No                            | No             | No                                                                                                                                                | Danger: 0 Warning: 0 Good: 0         |

| Trace to board edge (Detect traces too close to the board edge)                              | No                            | No             | No                                                                                                                                                | Danger: 0 Warning: 0 Good: 0         |

| Trace spacing (Measure spacing between adjacent parallel traces)                             | No                            | No             | No                                                                                                                                                | Danger: 0 Warning: 0 Good: 0         |

| Unconnected trace end (Free-standing trace ends not connected to pads)                       | No                            | No             | No                                                                                                                                                | Danger: 0 Warning: 0 Good: 0         |

| Trace width<br>(Trace width information)                                                     | 0.25mm<br><b>Good</b>         |                | Project Outputs for Barrel Jack DCDC Project\PCB2_Copper_Signal_Bot.g br Project Outputs for Barrel Jack DCDC Project\PCB2_Copper_Signal_Top.g br | Danger: 0<br>Warning: 0<br>Good: 15  |

| Fiducial (Detect fiducial marks on the board)                                                | No                            | No             | No                                                                                                                                                | Danger: 0<br>Warning: 0<br>Good: 0   |

| Pad to board edge (Measure distance of pads from the board edge)                             | No                            | No             | No                                                                                                                                                | Danger: 0 Warning: 0 Good: 0         |

| Pad spacing<br>(Measure pad to pad spacing)                                                  | 0.23mm<br><b>Good</b>         |                | Project Outputs for Barrel Jack DCDC Project\PCB2_Copper_Signal_Top.g br                                                                          | Danger: 0<br>Warning: 0<br>Good: 8   |

| Plated through-hole to trace clearance (Measure clearance of plated through-holes to traces) | No                            | No             | No                                                                                                                                                | Danger: 0<br>Warning: 0<br>Good: 0   |

| Annular ring (Annular ring width of pads compared to holes)                                  | No                            | No             | No                                                                                                                                                | Danger: 0<br>Warning: 0<br>Good: 0   |

| tht to smd<br>Detect clearance of vias to pads)                                              | 0.64mm<br><mark>Danger</mark> |                | Project Outputs for Barrel Jack DCDC Project\PCB2_Copper_Signal_Top.g br                                                                          | Danger: 33<br>Warning: 17<br>Good: 0 |

| Via to pad                                                                                   | No                            | No             | No                                                                                                                                                | Danger: 0                            |

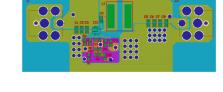

## PCB screenshot

PCB DFM>Soldermask layer analysis

No

No

Layer distribution

Warning: 0

Good: 0

Statistics

| Analyze project                                                                                                          | Analysis results | PCB screenshot | Layer distribution                                                   | Statistics                         |  |

|--------------------------------------------------------------------------------------------------------------------------|------------------|----------------|----------------------------------------------------------------------|------------------------------------|--|

| PCB DFM>Silkscreen layer analysis                                                                                        |                  |                |                                                                      |                                    |  |

| Negative soldermask expansion<br>(Detect solder mask openings<br>smaller than their corresponding<br>pads)               | No               | No             | No                                                                   | Danger: 0<br>Warning: 0<br>Good: 0 |  |

| Soldermask opening with multiple segments (Check if solder mask openings are constructed from multiple geometric shapes) | null<br>Warning  |                | Project Outputs for Barrel Jack DCDC Project\PCB2_Soldermask_Top.gbr | Danger: 0<br>Warning: 1<br>Good: 0 |  |

| Solder mask opening exposing trace<br>(Detect clearance of solder mask<br>openings to nearby traces)                     | No               | No             | No                                                                   | Danger: 0<br>Warning: 0<br>Good: 0 |  |

| Soldermask bridge (Detect distance between parallel soldermask opening edges)                                            | 0.15mm<br>Good   |                | Project Outputs for Barrel Jack DCDC Project\PCB2_Soldermask_Top.gbr | Danger: 0<br>Warning: 0<br>Good: 5 |  |

|                                                                                                                          |                  |                |                                                                      |                                    |  |

| Silkscreen to pad                                      |                 |                           |                                                                        | Danger: 0                            |

|--------------------------------------------------------|-----------------|---------------------------|------------------------------------------------------------------------|--------------------------------------|

| (Detect clearance of silkscreen to                     | No              | No                        | No                                                                     | Warning: 0                           |

| pads)                                                  |                 |                           |                                                                        | Good: 0                              |

| Silkscreen to hole                                     |                 |                           |                                                                        | Danger: 0                            |

| (Detect clearance of silkscreen to                     | No              | No                        | No                                                                     | Warning: 0                           |

| holes)                                                 |                 |                           |                                                                        | Good: 0                              |

| Silkscreen line width<br>(Check silkscreen line width) | 0.1mm<br>Danger |                           | Project Outputs for Barrel Jack<br>DCDC<br>Project\PCB2_Legend_Top.gbr | Danger: 10<br>Warning: 40<br>Good: 0 |

|                                                        | P               | CB DFM>Drill layer analys | is                                                                     |                                      |

| PCB DFM>Drill layer analysis                                                                               |                  |                |                    |                                    |  |

|------------------------------------------------------------------------------------------------------------|------------------|----------------|--------------------|------------------------------------|--|

| Analyze project                                                                                            | Analysis results | PCB screenshot | Layer distribution | Statistics                         |  |

| Missing plated through-hole (Detect top and bottom pads at the same location without plated through-holes) | No               | No             | No                 | Danger: 0 Warning: 0 Good: 0       |  |

| Plated through-hole spacing (Measure spacing between plated through-holes)                                 | No               | No             | No                 | Danger: 0<br>Warning: 0<br>Good: 0 |  |

| Short slot detection (Detect slots shorter than twice their width)                                         | No               | No             | No                 | Danger: 0<br>Warning: 0<br>Good: 0 |  |

| Slot width check<br>(Measure slot width)                                                                   | No               | No             | No                 | Danger: 0<br>Warning: 0<br>Good: 0 |  |

| Via to PTH spacing (Measure spacing of vias to plated through-holes)                                       | No               | No             | No                 | Danger: 0<br>Warning: 0<br>Good: 0 |  |

| Unconnected via                                                                                            |                  |                |                    | Danger: 0                          |  |

No

No

Warning: 0

Good: 0

No

(Detect isolated unconnected

vias)